International Journal of Research and Reviews in Applied Sciences And Engineering (IJRRASE) Vol 8. No.1 -2016 Pp.211-218 ©gopalax Journals, Singapore available at : www.ijcns.com ISSN: 2231-0061

## NOVEL DESIGN FOR BCD ADDER WITH MINIMIZED DELAY

S.Subathradevi<sup>#1</sup>, C.Vennila<sup>#2</sup>, R.Vishnupriya<sup>#3</sup>, B.Angalaeswari<sup>#3</sup>, M.Neethija<sup>#3</sup> <sup>#1</sup>Assistant Professor, Department of ECE, <sup>#2</sup>Professor, Department of ECE, <sup>#3</sup>Student, Department of ECE, <sup>#1</sup>Anna University-BIT Campus, Tiruchirappalli, India. <sup>#2</sup>Saranathan College of Engineering, Panjapur Tiruchirappalli, India. <sup>#3</sup>Student, Anna University-BIT Campus, Tiruchirappalli, India.

ABSTRACT— In VLSI design of system reducing the number of gates and garbage architecture configuration, the speed is purely determined by the delay of the design. In the delay of the design, it is mainly depending on the routing i.e. path delay. Nowadays in the design, the path or routing delay dominates more towards the design delay when compare to the earlier days where gate delay dominates more towards the design delay. So, it is essential to concentrate more towards routing delay of the design to achieve the optimum speed of the architecture.

In this work, by studying different architectures of BCD adder which is being constructed with different sub-modules which contributes towards the delay estimation, which are realized and implemented on the FPGA.

designed BCD Adder is using reversible gates to reduce delay. A new design of reversible BCD adder having C0 as input carry with no ancilla input bits gives less quantum cost and logic depth. The reversible logic gates find its application like low power CMOS, quantum computing, nano technology and optical computing because of its zero power dissipation. It is done by

# outputs.

KEYWORDS-BCD Adder. Architecture. Macro, VLSI, routing delay, ancilla input bits, reversible logic gates.

## **I. INTRODUCTION**

For any system design, the arithmetic units are much important to make it as a successful design. In arithmetic unit adders took more contribution to play a vital role since subtraction and multiplication are computed only by means of addition. So, if the speed is achieved by minimizing the delay, in the delay of the architecture of adder and multiplier surely it leads to a better performance in the speed of the design of the high speed system. So, various architectures BCD adder are realized. implemented and their delay is compared.

In modern VLSI system due to rapid switching of internal signals, power dissipation is high. The amount of heat energy is generated in irreversible logic, the computation is easy. Reversible gates do not lose information during logic computation which virtually dissipates zero heat. Adders are fundamental building blocks in many computational units. It is an easy conversion to digital digits for printing and display faster calculations. One of the major problems with reversible logic is fan out and feedback cannot be used. According to Moore's law, the number of transistors will double in every 18 months.

Today the most important feature in BCD adder is to conserve energy. Binary computing is used in hardware design because of ease in building hardware when compared with decimal computing. This binary computing is not suited for financial and commercial because it cannot tolerate errors. In classical computing usage of digital data using logical operations. In this a single bit of information is erased after every logical operation. Improvement in technology leads to compact size and increase in execution speed. High level of integration and the use of new fabrication process have reduced in the Genetic Algorithms used to synthesize and optimize logic circuit. At present irreversible technologies can reduce the life of the circuit and also dissipate more heat. But in reversible logic operations it does not lose any information and dissipate very less heat.

This paper is organized as follows. Section I says about the Introduction. Section II deals about BCD adder, Section III deals with Literature Survey ,Section IV deals with proposed Architecture, Section V deals with experimental results obtained, while Section VI deals with Conclusion and Discussion.

#### **II. BCD ADDER**

The BCD code is a code that combines the features of decimal and binary base number system. In BCD number system a group of binary bit is used to represent each of 10 decimal digits.

BCD numbers are used to transfer the decimal information into a Computer, Packet calculators, electronic counters, digital voltmeters and digital clocks are the applications of BCD numbers. BCD code referred to as 8421 code. Instead of using all combinations (0-15) of only code use (0-9) combinations. 1001 is the largest number in BCD number system. Other numbers 1010.1011.1100.1101.110 and 1111 are not used because these are all considered as forbidden.1001 is the largest 4-bit group in the BCD code. BCD adder is a 4-bit binary adder that is capable of adding two fur bit words having a BCD.

Fig.2 Table for BCD addition.

| ĸ | 3lpa | ry ' | Sur<br>4Z | n<br>27 1 | BC | D <sub>S</sub> | Sun<br>s S | 45 | 251 | Decimal |

|---|------|------|-----------|-----------|----|----------------|------------|----|-----|---------|

| 0 | 8    | 0    | 0         | 0         | 0  | 0              | 0          | 0  | 0   | 0       |

| 0 | 0    | 0    | 0         | 1         | 0  | 0              | Ū.         | 0  | 1   | 1       |

| 0 | 0    | 0    | 1         | 0         | 0  | Ū              | 0          | 1  | Π   | 2       |

| 0 | 0    | 0    | 1         | 1         | 0  | 0              | 0          | 1  | 1   | 3       |

| 0 | 0    | 1    | 0         | 0         | 0  | 0              | 1          | 0  | 0   | 4       |

| 0 | 0    | 1    | 0         | 1         | 0  | 0              | 1          | 0  | 1   | 5       |

| 0 | 0    | 1    | 1         | 0         | 0  | 0              | 1          | 1  | 0   | 6       |

| 0 | 0    | 1    | 1         | 1         | 0  | 0              | 1          | 1  | 1   | γ.      |

| 0 | 1    | 0    | 0         | 0         | o  | 1              | 0          | 0  | 0   | 8       |

| 0 | 1    | 0    | 0         | 1         | 0  | 1              | 0          | 0  | 1   | 9       |

| 0 | 1    | 0    | 1         | 0         | 1  | 0              | 0          | 0  | 0   | 10      |

| 0 | 1    | 0    | 1         | 1         | 1  | 0              | 0          | 0  | 1   | 11      |

| 0 | 1    | 1    | 0         | 0         | 1  | 0              | 0          | 1  | 0   | 12      |

| 0 | 1    | 1    | 0         | 1         | 1  | 0              | 0          | 1  | 1   | 13      |

| 0 | 1    | 1    | 1         | 0         | 1  | 0              | 1          | 0  | 0   | 14      |

| 0 | 1    | 1    | 1         | 1         | 1  | ۵              | 1          | 0  | 1   | 15      |

| 1 | 0    | 0    | 0         | 0         | 1  | 0              | 1          | 1  | 0   | 16      |

| 1 | 0    | 0    | 0         | 1         | 1  | 0              | 1          | 1  | 1   | 17      |

| 1 | 0    | 0    | 1         | 0         | 1  | 1              | 0          | 0  | 0   | 18      |

| 1 | 0    | 0    | 1         | I         | 1  | 1              | 0          | 0  | 1   | 19      |

Example1: Augent 0110(6) Addent 0101(5) Sum 1011(11) (Invalid BCD Number) Add 0110(6) BCD 10001(11) (Valid BCD Number) Answer 0001 0001(11) Example2: Augent 0011(3) Addent 0110(6) Sum 1001(9) (Valid BCD Number) Add 0000(0) BCD 1001(9) (Valid BCD Number) Answer 0000 1001(9)

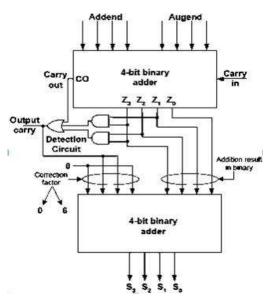

Reversible logic is used in computing applications and by reducing size and hence portability of the devices are increase. The result of the addition is in a BCD format four bit output word representing the decimal sum of the Addend & Augent and a carry that is generated. If this sum exceeds a decimal value of nine, decimal addition is the required possibility using the correction circuit. BCD addition is same as binary addition when the result of the addition is same as binary addition when the result of the addition is beyond 9(1001), we must add 6(0110) to the original result. So two 4 bit parallel adders are used to get correct result. One of the adders is used to add the given BCD numbers. Second adder is first to determine the result of the previous one whether it exceeds the BCD range or not. If it is exceeding 0110 is added to the previous result. The result of the second adder is to generate the correct BCD output.

### **III. LITTERATURE SURVEY**

Improving efficiency is achived by use of this logic.Moreover it will affect the speed of the circuits such as nano circuits and computing applications.[1], Reversible logic circuits are constructed under two constrains(Fan-Out and loops/feedback) which are not permitted. It may be used along with other parameters such as constants. garbage, gate count, flexibility, quantum cost, gate levels which may optimize the circuit effectively.[2], The aim of this paper is to perform both BCD addition/subtraction is a single circuit. For this reason two new optimized gates are used which does not provide any restrictions. To operate this garbage output, gate count and constant input should be minimum.[3], The main focus of this paper is low power dissipation under 70nm technology by using RPS with BCD adder.[4], To obtain exact BCD value, the modified circuit which is the combination of parallel adder and overflow detection circuit is used.[5]

#### **IV.PROPOSED ARCHITECTURE**

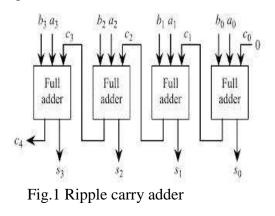

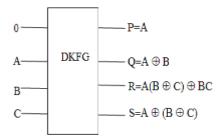

Fig DKFG GATE

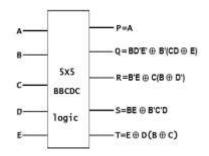

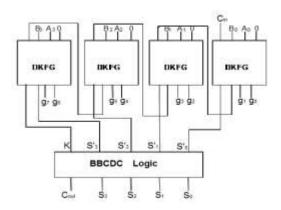

## Fig BBCDC LOGIC

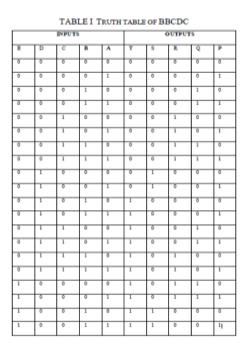

Fig Table of BBCDC LOGIC

Fig BCD ADDER using Reversible Gates

## **V. RESULT**

# BCD ADDER USING BINARY ADDER AND

### **CORRECTION CIRCUIT**

| DIGIT                      | 1      | 2      | 1      | 4        | 3      |

|----------------------------|--------|--------|--------|----------|--------|

| NUMBER OF<br>SLICES        | 9      | 18     | 26     | 35       | 44     |

| NUMBER OF<br>LUTs          | 32     | 62     | 92     | 122      | 152    |

| AREA                       | 41     | 80     | 118    | 157      | 196    |

| COMBINATIONAL<br>DELAY(ns) | 14.466 | 20.038 | 25.432 | 30.826   | 36.220 |

| FREQUENCY(MHZ)             | 69.127 | 49.905 | 39.320 | 32,440   | 27.609 |

| POWER(mm)                  | 0.081  | 0.081  | 0.081  | 0.081    | 0.081  |

|                            |        | 0.00   |        | - 10 M M |        |

### **BCD ADDER USING NAND ONLY GATES**

| DIGIT                      | 1      | 2      | 3      | 4      | 5      |

|----------------------------|--------|--------|--------|--------|--------|

| NUMBER OF<br>SLICES        | 14     | 25     | 38     | 50     | 63     |

| NUMBER OF<br>LUTs          | 48     | 90     | 134    | 178    | 222    |

| AREA                       | 62     | 115    | 172    | 228    | 285    |

| COMBINATIONAL<br>DELAY(ns) | 12.928 | 17.728 | 23.732 | 29.552 | 35,372 |

| FREQUENCY(MHZ)             | 77.351 | 56.407 | 42.137 | 33.838 | 28.270 |

| POWER(mw)                  | 0.081  | 0.081  | 0.081  | 0.081  | 0.081  |

## **BCD ADDER USING REVERSIBLE LOGIC** GATES

| DIGIT                          | 1       | 2      | 3      | 4      | 5      |

|--------------------------------|---------|--------|--------|--------|--------|

| NUMBER OF<br>SLICES            | 9       | 18     | 27     | 36     | 43     |

| NUMBER OF<br>LUTA              | 32      | 64     | 96     | 128    | 160    |

| AREA                           | 41      | 82     | 129    | 164    | 205    |

| COMBENATION<br>AL<br>DELAY(ns) | 9.419   | 13.481 | 17.543 | 21.605 | 25.667 |

| FREQUENCY(M<br>HZ)             | 106.168 | 74,178 | 57.002 | 46.285 | 38.960 |

| POWER(mw)                      | 0.081   | 0.061  | 0.081  | 0.081  | 0.081  |

## BCD ADDER DESIGN USING MULTIPLEXER

| DIGIT                          | 1      | 2      | 1.1    | 4      | 3      |

|--------------------------------|--------|--------|--------|--------|--------|

| NUMBER OF<br>SLICES            | 9      | 18     | 26     | 35     | 43     |

| NUMBER OF<br>LUTs              | 32     | 62     | 92     | 122    | 152    |

| AREA                           | 41     | 80     | 118    | 157    | 195    |

| COMBINATIO<br>NAL<br>DELAY(ns) | 14.295 | 20.084 | 25,478 | 30.872 | 36.226 |

| FREQUENCY(<br>MHZ)             | 69.954 | 49.790 | 39.249 | 32,391 | 27,604 |

| POWER(mw)                      | 0.081  | 0.081  | 0.081  | 0.081  | 0,081  |

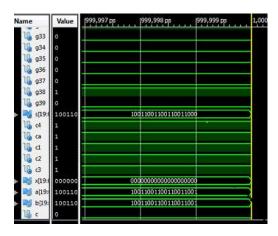

### SIMULATION OUTPUT FOR BCD ADDER DESIGN USING REVERSIBLE GATES (5-DIGIT)

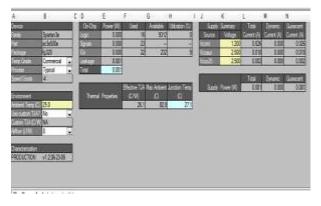

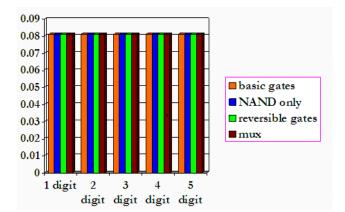

## **POWER OUTPUT (5-DIGIT)**

### PICTOGRAPH

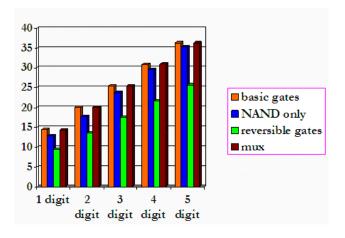

### **DELAY COMPARISON CHART**

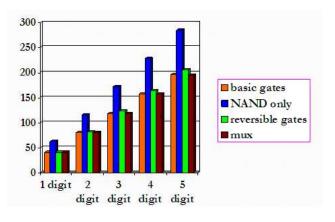

### **AREA COMPARISON CHART**

| DELAY(ns) | AREA                       | POWER(mw)                                                                    |

|-----------|----------------------------|------------------------------------------------------------------------------|

| 36.226    | 196                        | 0.081                                                                        |

| 35.372    | 285                        | 0.081                                                                        |

| 25.667    | 205                        | 0.081                                                                        |

| 36.226    | 195                        | 0.081                                                                        |

|           | 36.226<br>35.372<br>25.667 | 36.226         196           35.372         285           25.667         205 |

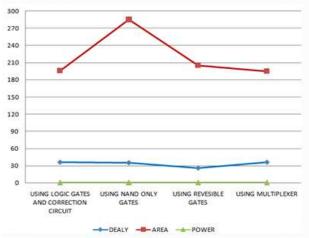

### PARAMETER COMPARISON CHART

#### POWER COMPARISON CHART

### **COMPARISON TABLE FOR 5 DIGITS**

### VI.CONCLUSION AND DISCUSSION

In this project work we have designed four architectures of BCD ADDER for primarily optimizing the parameter like delay, area and power. These architectures Compute BCD addition up to 5 digits.

The optimization of delay in BCD ADDER using REVERSIBLE GATES is mainly considered to lesser delay. Even though various architectures are constructed in this project work, BCD ADDER using REVERSIBLE GATES gives 29% less delay compared to BCD ADDER using BINARY ADDERS and CORRECTION CIRCUIT. Getting 27% delay reduction when compared to BCD ADDER using NAND ONLY gates and 29% delay is reduced compared with BCD ADDER using MULTIPLEXER.

Finally we concluded that lesser delay is achieved using BCD ADDER using REVERSIBLE GATES among all the above mentioned architectures.

### REFERENCES

- [1] S.R.Pradeep, Praveen Kumar and S.R.Prathibha, "Low Power and High Speed BCD ADDER using Reversible Gates", International Journal of Electronics, communications & soft computing science and engineering, ISSN : 2277-9477, volume 2, Issue 9.

- [2] Shefali Mamataj, Biswajit Das and Anurima Rahaman, "A More Effective Realization of BCD Adder by using a New Reversible Logic BBCDC", International Journal of computational Engineering Research, volume 4, Issue 2.

- [3] S.B.Rashmi, B.Praveen and B.G.Tila, "Design of Optimized Reversible BCD Adder/subtractor", IACSI7 International Journal of Engineering and Technology, volume 3, No.3, June 2011.

- [4] C.Mounesh Kumar, M.Srinivasullu,

S.Ahmed Basha, K.Suvarna and

H.Devanna, "Design of Low Power 4-Bit

BCD adder using Reversible Gates",

Department of ECE, SJCET.

- [5] Umana Thompson Itaketo, "A Modified Logic Circuit of BCD Adder to Overcome the "Carry" Problems", Department of Electrical/Electronics and Computer Engineering, University of

Uyo, Uyo, Nigeria.

- [6] B.B.Manjula, Venkatesh S.Sanganal, K.N.Hemalatha and V.Ravichandren, "FPGA Implementation of optimized 4 Bit BCD and carry skip Adders using Reversible Gates" International Journal of soft computing and engineering (IJSCE), ISSN : 2231-2307, Issue 3, July 2012.

- [7] M.Rajmohan and D.Sahaya lenin, " A Novel Design of carry skip Adder using Reversible Gates", International journal of computer applications, ISSN : 0975-8887, volume 73, No.6, July 2013.

- [8] Md.Sazzad Hosssain. Md.Rashedul Rakib, Hasan Md.Motiur Rahman. A.S.M.Delowar Hossain and Md.Minul Hasan, "A New Design Technique of Reversible BCD Adder Based on NMOS With Pass Transistor Gates". International Journal of VLSI Design and Communication Systems (VLSICS), Volume 2, No.4, December 2011.

- [9] Himanshu Thapliyal and Nagarajanarajan Ranganathan, "Design of Efficient Reversible Logic Based Binary and BCD Adder Circuits", University of South Florida, Tampa

- [10] Majid Mohammadi, Mohammed Eshghi, Majid Haghparast and Abbas Bahrololoom,"Design and Optimization of Reversible BCD Adder/Subtractor Circuit for Quantum and Nanotechnology Based Systems", World Applied Sciences Journal 4(6):787-792, ISSN:1818-4952, IDOSI Publications, 2008.

- [11] Md.Saiful Islam, Mohd.Zulfiquar

Hafiz and Zerina Begum, "Quantum Cost Efficient Reversible BCD Adder for Nanotechnology Based Systems", International Journal of Computer and Electrical Engineering, Volume 4, No.1, February 2012.

- [12] S.Rambabu, B.Sruthi, K.Sreelakshmi, V.Ramyakrishna, S.Althaf and K.Subash, "High Performance and Low Noise BCD Adder Circuit Design Using Rate Sensing Keeper", International Journal of Advanced Research in Electrical. Electronics Instrumentation and Engineering, Volume 4, Issue 4, April 2015.

- [13] H.Bhagya Laxmi, T.R.Prasuna Barre, "Low Leakage and Power Saving 4-Bit BCD Adder", International Journal Of Scientific Research And Education", ISSN:2321-7545, Volume 2, Issue 12, December 2014.

- [14] Ruchi Gupta and Shivangi Tyagi,

" VLSI Implementation of Optimized Reversible BCD Adder", Conference on Advances in Communication and Control Systems, 2013.

- [15] N.A.Shah, F.A.Khanday and Z.A.Bangi, " Quantum Cellular Automata Based Efficient BCD Adder Structure", Department of Electronics and Instrumentation Technology, University of Kashmir, Srinagar.

- [16] C.Sundaresan, CVS.Chaitanya, PR.Venkateswaran, Somashekara Bhat and J.Mohan Kumar, "Design and Development of Vedic Mathematics based BCD Adder", Internationl Journal of Applied Information Systems (IJAIS), ISSN:2249-0868, Volume 6, No.9,

March 2014.

- [17] T.S.R.Krishna Prasad and Y.Satyadev, "An Efficient Reversible Design of BCD Adder", International Journal of Computer Technology and Applications, ISSN:2229-6093, Volume 3(5).

- [18] Sreehari Veeramachaneni,

M.Kirthi Krishna, Lingamaneni Avinash,

P.Sreekanth Reddy and M.B.Srinivas,

"Novel, High Speed 16-digit BCD

Adders Conforming to IEEE 754r

Format", Centre for VLSI and Embedded

System Technologies (CVEST),

International Institute of Information

Technology, Hyderabad.

- [19] Muniraja Thoti and M.Jagadeeshwar Reddy, "Design of Low Power BCD Adder Using 14-T Full Adder", International Journal of Engineering Research and Applications (IJERA), ISSN:2248-9622, Volume 3, Issue 4, July-August 2013.

- [20] C.Sundaresan, CVS.Chaitanya, PR.Venkateswaran, Somashekara Bhat and J.Mohan Kumar, "Design and Synthesis of Reduced Delay BCD ", Internationl Journal of Computer and Information Technology, ISSN:2279-0764, Volume 4, Issue 1, January 2015.